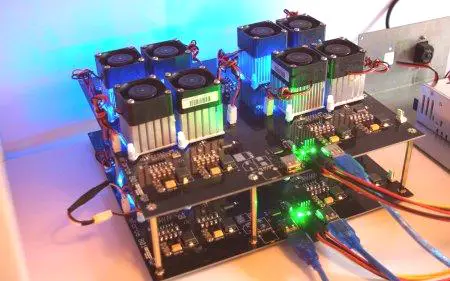

FPGA pomeni "Field Programmable Gate Array" in predstavlja veliko paleto ventilov, ki jih je mogoče programirati in obnoviti kadarkoli in kjerkoli. Mnogi uporabniki še vedno ne razumejo, kaj je FPGA. "Velik nabor vrat" - poenostavljen opis modela. Nekatere FPGA imajo vgrajene trde diske: krmilnike pomnilnika, hitre komunikacijske vmesnike in končne točke PCIe. V notranjosti FPGA je veliko ventilov, ki jih je mogoče prosto povezati. Načelo dela je bolj ali manj podobno povezavi posameznih čipov logičnih elementov. FPGA izdelujejo vodilna podjetja na svetu, Xilinx, Altera in Microsemi.

Zgodovina razvoja FPGA

Industrija FPGA je zrasla iz programiranega trajnega pomnilnika PROM in logičnih naprav PLD. Leta 1970 je Philips izumil matriko, ki jo je mogoče programirati na terenu. Pri načrtovanju takega FPGA, ki je sestavljen iz dveh načrtov, je bila dosežena specifična izvedba logičnih vezij: funkcionalno žično "I" ali "OR". To ji je dalo priložnost za izvajanje funkcije v obliki vsote izdelkov.

Altera je bila ustanovljena leta 1983, leta 1984 pa je izdelala prvo v industriji, ki lahko reprogramira logično napravo - EP300 s kvarčnim oknom v paketu, kar je omogočilo uporabo ultravijolične žarnice na matriki za odstranitev oznake EPROM. Da bi premagali težave s stroški in hitrostjo, je bila razvita programabilna logika matrike, ki je vključevala samo en programabilni "I", vnesen v fiksna vrata "OR". PAL inPLA, skupaj z drugimi različicami, so združeni v enostavne programljive SPLD logične naprave. Takšna FPGA, integrirana v en čip z zagotovljenimi povezavami za povezavo blokov s programsko opremo, so bila uporabljena za izpolnjevanje naraščajočih tehnoloških zahtev. Imenujejo se integrirani PLD-ji in jih je razvila družba Altera.

Tranzistorji - drugi razred elektronskih naprav, ki temeljijo na programabilnih maskah vratnih nizov. Sestavljeni so iz tranzistorskih nizov, ki jih je mogoče povezati z uporabniškimi žicami. Umaknili so se logičnim blokom, zdaj pa se lahko uporabnik nastavi na mestu, ne v proizvodnem laboratoriju. Ideja razvoja prvega komercialno uspešnega FPGA sodi med soustanovitelje Xilinxa Rossa Freemana in Bernarda Wondershmitta. XC2064 je izumljen leta 1985 in je sestavljen iz 64 prilagodljivih logičnih blokov s 3 referenčnimi tabelami. Zagotavlja sodobno razumevanje tega, kaj je FPGA. To je bilo konec leta 1980, ko je Steve Casselmanov eksperiment pri ustvarjanju računalnika s 600.000 reprogramiranimi vrati našel sponzorje v Oddelku za mornariško vojno mornarice Združenih držav, nato pa je leta 1992 prejel patent.

Do konca leta 1990 je prišlo do velike konkurence v proizvodnji FPGA, nato pa se je tržni delež Xilinxa začel zmanjševati. Igralci, kot so Actel, Altera, Lattice, QuickLogic, Cypress, Lucent in SiliconBlue, so poleg Xilinxa prevzeli nišo na svetovnem trgu FPGA. Leta 1997 je Adrian Thompson uspel združiti programiranje FPGA in tehnologijo genetskega algoritma s FPGA, začenši z novo dobo Evolvable.

Danes je FPGA postala dovoljdostopen, zato še naprej pridobiti popularnost na potrošniških trgih. Sestavljeni so iz niza logičnih celic, ki se imenuje iskalna tabela LUT, obdan mezhkomponentnoy omrežje, ki omogoča prilagodljiv sistem, ki se lahko izvajajo praktično vse digitalne algoritem.

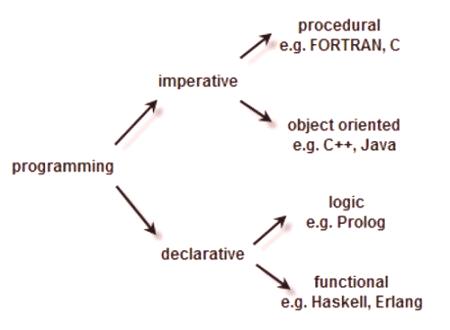

Načela programiranja

FPGA programiranje za začetnike - proces raziskave, načrtovanje, projektiranje in izvedbo rešitev na FPGA. Število in vrsta načrtovanja se razlikujejo od programa do programa. Ustvari dokument z zahtevami in oblikovanje novega dokumenta, ki pojasnjuje, kako bo predlagana rešitev izvajajo, je lahko zelo koristno za reševanje morebitnih težav.

Čas, porabljen za ustvarjanje kakovostnega oblikovanja dokumenta, ga shranite v prihodnjih refactoring, odpravljanje napak in popravke napak. Izvajanje rešitev skozi FPGA programiranja vključuje ustvarja projekt z uporabo enega od načinov izvedbe. Med temi shemami ali kode HDL, na primer, Verilog ali VHDL. FPGA lahko nastavite izhodno datoteko na fizično FPGA programskih naprava orodij z uporabo FPGA Altera. Uvod v načrtovanje vezij se ne uporablja več v industriji uporabljajo. Sinteza in programiranje je skoraj v celoti poskrbljeno ponudnikov orodij, konfiguracije orodja, kot ISE in Vivado in Numato Lab.

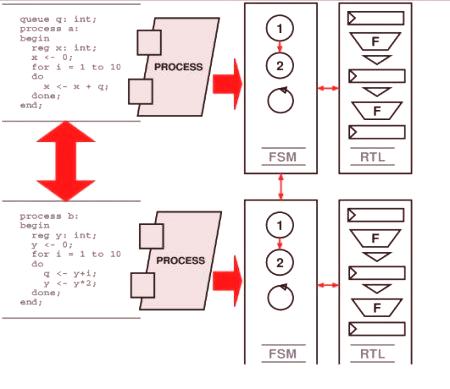

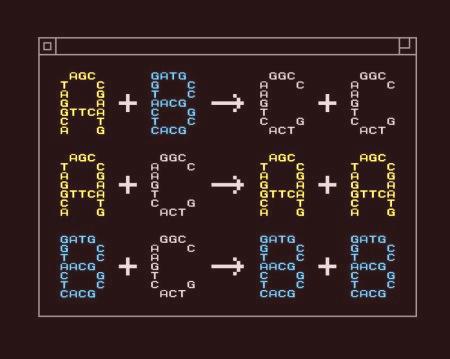

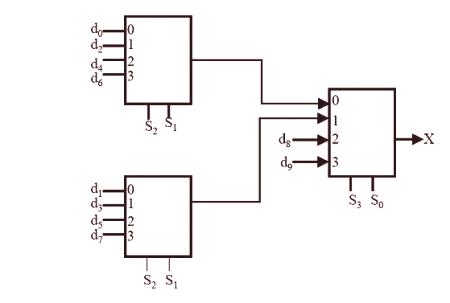

Stopnja prenos Register RTL

Stopnja RTL kaže primer prenosa. Razvijalec lahko tudi naletijo pogoji Registriraj Transfer Logic ali Registriraj Transfer jezik, pomenijoisto stvar pri načrtovanju opreme. RTL je abstrakcija višje ravni za oblikovanje digitalne strojne opreme, ki se nahaja nekje med strogo vedenjsko simulacijo na enem koncu in povsem strukturno na ravni prehoda - na drugi. Simulacija vrat pomeni opis strojne opreme z uporabo osnovnih ventilov, ki je precej oslabljen. RTL je mogoče obravnavati kot analog izraza "psevdo-koda", ki se uporablja v programskem okviru FPGA. Načrtovanje strojne opreme lahko opišete kot zaporedje korakov ali podatkovnih tokov iz enega niza registrov na naslednji v vsakem taktnem ciklu. RTL se imenuje tudi "tok podatkov". Takoj, ko je projekt RTL pripravljen, ga je lažje pretvoriti v resnično kodo HDL z uporabo jezikov, kot so Verilog, VHDL, SystemVerilog ali kateri koli drug jezik strojne opreme. FPGA je veliko več kot le niz vrat. Čeprav je mogoče zgraditi logične sheme poljubne kompleksnosti, organizirati in povezati logične elemente. To je način za izražanje logike v preprostem formatu, ki se lahko sčasoma spremeni v niz elementov. Dve popularni metodi tega sta: uvedba sheme in opis jezika opreme HDL. Preden se je širše uporabljal, so inženirji vse zasnovali s pomočjo shem. Bili so zelo preprosti za majhne projekte, a boleče brez upravljanja - za velike. Predstavljajte si, kako Intelovi inženirji pripravijo vezje za Pentium z milijoni prehodov! To je nesprejemljivo težko.

Verilog je opis strojne opreme HDL, ki jo lahko uporabitedigitalna vezja v besedilni obliki. Učenje Verilog ni tako težko, če ima uporabnik izkušnje s programiranjem. VHDL je še en priljubljen HDL, ki se pogosto uporablja v industriji. Verilog in VHDL-ji imata bolj ali manj enako priznanje na trgu, vendar uporabniki običajno izberejo Verilog, ker se ga je enostavno naučiti in ima skladenjsko podobnost z jezikom C.

Tehnologije programiranja

FPGA se lahko štejejo kot gradniki, ki omogočajo pravilno nastavitev opreme. To je posebna oblika PLD z večjo gostoto in razširjeno funkcionalnostjo v krajšem časovnem obdobju z uporabo CAD. FPGA so na voljo v različnih različicah, ki temeljijo na uporabljeni tehnologiji programiranja. Lahko jih programirate z:

tehnologijo za zaščito pred preobremenitvijo. Programiranje, ki temelji na tehnologiji naprave Flash iz Actela. FPGA je mogoče reprogramirati več tisočkrat, kar traja nekaj minut na samem polju za reprogramiranje in ima trajni pomnilnik.FPGA na osnovi SRAM, ki ponuja neomejeno reprogramiranje in zelo hitro rekonfiguracijo ali delno rekonfiguracijo med samim delom z majhnim številom dodatnih vezij. Večina teh podjetij, kot so Altera, Actel, Atmel in Xilinx, proizvajajo te naprave.

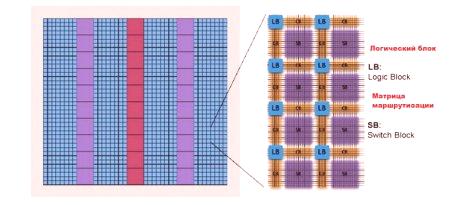

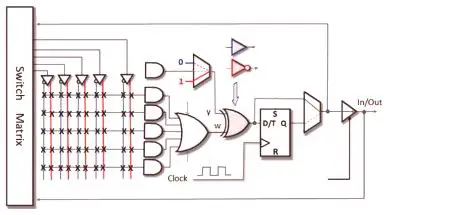

Konfigurirani logični bloki

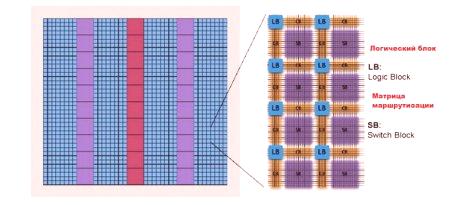

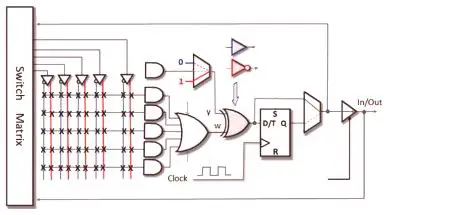

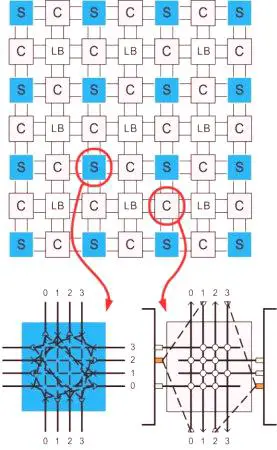

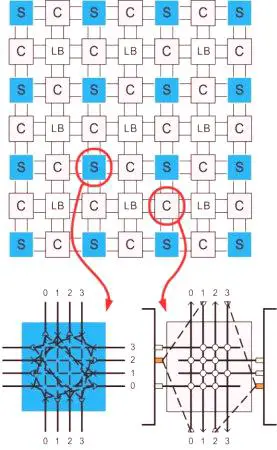

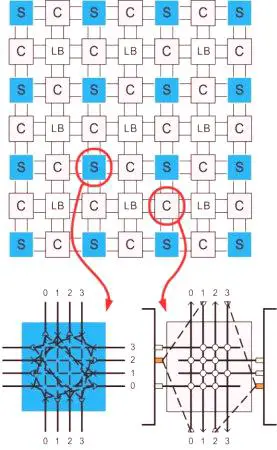

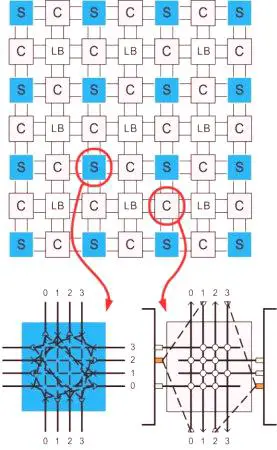

Ne glede na različne proizvajalce in več različnih arhitektur in funkcijskih sklopov ima večina FPGA skupen pristop. Glavni komponentni bloki FPGA so prilagodljivi programabilni "logični blok" (CLB), obdan z programabilnimi "bloki"I /O "s hierarhijo usmerjevalnih kanalov, ki povezujejo različne bloke na plošči.

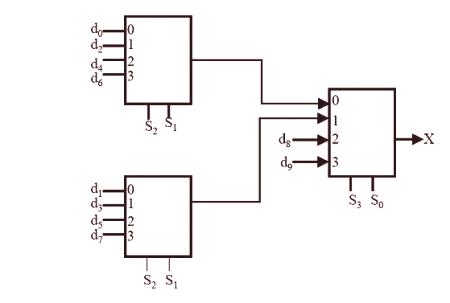

Poleg tega so lahko sestavljeni iz DLL-jev za dodeljevanje in krmiljenje ur in RAM izbranega bloka z glavnim gradivom logične celice. Slednji je sestavljen iz generatorja vhodnih funkcij, logike prenosa in shranjevanja elementov. Generatorji se izvajajo v obliki referenčnih tabel in so odvisni od vhoda. Na primer, Xilinx Spartan II ima 4 vhodne LUTs, ki zagotavljajo vsak 16X1-bitni sinhroni RAM z uporabo multipleksorjev kot izmenjevalni registri za zajem podatkov v paketnem načinu. Elementi za shranjevanje so občutljivi na robove sprožilcev ali na raven ključavnic. Razdrobljenost FPGA:

Aritmetična logika vključuje prehod XOR za delo s popolnim seštevalnikom in dodeljevanje logičnih prenosnih linij. Blok I /O in matrika usmerjanja. Ta enota ima vhode in izhode, ki podpirajo širok spekter standardov in vmesnikov za signalizacijo.Spodaj je prikazan osnovni V /I blok. Medpomnilnik pod vhodnimi in izhodnimi potmi pošilja signale notranji logiki in končni platformi neposredno ali skozi sprožilec. Konfigurirani so tako, da ustrezajo različnim podprtim alarmnim standardom, ki jih lahko določi uporabnik in jih namestijo od zunaj.

Matrica za usmerjanje

Na vsakem tekočem traku počasen segment določa splošno zmogljivost. Usmerjevalni algoritmi se uporabljajo za razvoj najučinkovitejših načinovzagotavljanje optimalne učinkovitosti. Usmerjanje se izvaja na različnih ravneh, kot je lokalno, splošno usmerjanje med različnimi CLB, I /O usmerjanje med bloki in CLB, namensko usmerjanje za določene razrede signalov za povečanje produktivnosti in Global Routing za merjenje urnih in drugih signalov z zelo velikimi razvejanostmi. . Družine FPGA imajo tudi veliko blokovno strukturo RAM-a, ki dopolnjuje porazdeljeno LUT RAM, velikost katere se razlikuje za različne FPGA naprave.

Oblikovanje FPGA vključuje v bistvu enak pristop kot vsak sistem VLSI, katerega glavne faze so načrtovanje, simulacija vedenja, sinteza, simulacija po sintezi, oddajanje, kartiranje in usmerjanje, kot tudi nadaljnja analiza, kot je sinhronizacijska simulacija. in statična sinhronizacijska analiza. Na računalniku je videz urejen in urejen, toda v resnici je nepopolna postavitev in usmerjanje, kar vodi do zmanjšanja zmogljivosti. Vedno lahko uporabite več tranzistorjev za povečanje zmogljivosti FPGA. Področje je visoko. Namestitev več tranzistorjev pomeni, da so možni veliki modeli. Uhajanje je resen problem za FPGA in je hkrati zanimivo. Uporaba asinhrone arhitekture FPGA kaže boljše rezultate v kombinaciji s transportno tehnologijo, ki zmanjšuje globalne vnose in izboljšuje pasovno širino.

Kakovost in vprašanja vrat

Varnost sistema je bila vednoglavni problem, saj je treba kodo odpreti vsakič, ko se naloži v FPGA. Ta prilagodljivost omogoča FPGA potencialno grožnjo zlonamernim spremembam v proizvodnem procesu, zato je šifriranje tokov bitnega toka prišlo v njegovo pomoč pravočasno. Pogosto neizkušeni oblikovalci in uporabniki se soočajo z dilemo, kako močna je FPGA za njihov razvoj. Proizvajalci pogosto navedejo meritve, na primer "število vrat". Na primer, programiranje Xilinx FPGA uporablja 3 metrike za merjenje FPGA volumnov, največje logične elemente, največje število pomnilnikov in tipično vrsto prehodov. Medtem ko so dosledne, je migracija med modeli nekoliko poenostavljena, vendar redko ponuja natančne primerjave med različnimi ponudniki zaradi raznolikosti v arhitekturi in zaradi razlik v učinkovitosti. Najboljši kazalnik je primerjava vrste in količine zagotovljenih logičnih virov. Poleg tega mora razvijalec v celoti razumeti, kaj natančno je potrebno od naprave, saj se lahko proizvajalci ponašajo s funkcijami, ki bodo najmanj pomembne za delo. Na primer, Altera Stratix II EP2S180 ima približno 186576 LUTs s 4 vhodi, in Xilinx Virtex-4 XC4VLX200 vsebuje 178176. Vendar, če projektiranje zahteva le 177.000 LUTs, bo to dovolj.

Če je RAM želena metrika za oblikovalca, potem niti 6 Mbit Xilinx XC4VLX200 niti 9 Mbit Altera EP2S180 ne bosta boljša od manj oglaševanega starejšega modela XC4VFX140 z 99 Mbit.

Programski jeziki in programska oprema

Programiranje FPGA Altera za začetnike se začne z izbiro jezika. Možnost C, C ++ aliSistem C vam omogoča uporabo zmožnosti največjih naprav in hkrati doseganje podobnosti realistične razvojne grafike. Zmožnost uporabe C-zasnovanega dizajna za FPGA zagotavlja HLS (sinteza na visoki ravni), ki je že vrsto let na prehodu z orodjem, kot je Handle-C. v zadnjem času je postala resničnost zaradi dejstva, da veliki dobavitelji Altera in Xilinx ponujajo HLS v svojih orodjih Spectra-Q in Vivado HLx. Na voljo je še nekaj drugih programskih izvedb programa Altera FPGA za začetnike, ki temeljijo na C, kot je OpenCL, ki je namenjen razvijalcem programske opreme, ki želijo povečati produktivnost z FPGA brez globljega razumevanja oblikovanja FPGA. Kot pri HDL, ima HLS omejitve pri uporabi FPGA programskih pristopov k C, kot pri tradicionalnih HDL, razvijalci morajo delati s podmnožico jezika. Na primer, težko je sintetizirati in izvajati sistemske klice, saj se morate prepričati, da je vse omejeno in da ima določeno velikost. V HLS je lepo, da lahko oblikujete svoje lastne algoritme s plavajočo vejico in obstaja orodje za pretvorbo HLS s plavajočo vejico v fiksno. Programiranje FPGA z Xilinxom sploh ni težko. Lahko ga dobite z nakupom izdelkov Xilinx brezplačno ali po modelu, specifičnem za ceno. Do videoposnetka lahko dostopate na spletnem mestu profila, ki jasno prikazuje postopek uporabe. Od vseh podjetij, ki jih je mogoče izbrati pri iskanju programirljivih nizov, je Xilinx zagotovo najboljši od vseh. So ustvarjalci tega izdelka in večveliko let ga je izboljšalo. Firmware je postal močnejši kot kdajkoli prej.

Faze načrtovanja

Programiranje FPGA se lahko izvaja na spletu, saj je platforma dobro predstavljena na internetu. Pri nastavitvi FPGA je prvi korak pri oblikovanju vezja, za katerega je potrebno znanje digitalne elektronike. Za razliko od programiranja je veliko težje začeti rezati kodo, če arhitektura programa ni jasna. Takoj ko postane jasno, da je potrebno izvajati, začnite opisovati shemo z uporabo enega od jezikov: Verilog ali VHDL. Dejstvo, da se paradigma spreminja, je, da se ne imenujejo programski jeziki FPGA, temveč so jeziki opisa. Zaradi zapletenosti testiranja digitalnih vezij banke običajno na tej stopnji uporabljajo teste, ki simulirajo obnašanje opreme. Ta vrsta orodja vam omogoča, da kadarkoli vidite stanje signala in preverite, ali obstajajo prehodi z želenimi rezultati.

Tretja faza, znana kot sinteza sheme, je ena od ključnih. Izbere uporabljene elemente in njihove medsebojne povezave v skladu z opisnimi datotekami. Za to stopnjo potrebujete orodja, ki v večini primerov poenostavljajo in avtomatizirajo naloge.

Strojna oprema in razhroščevanje

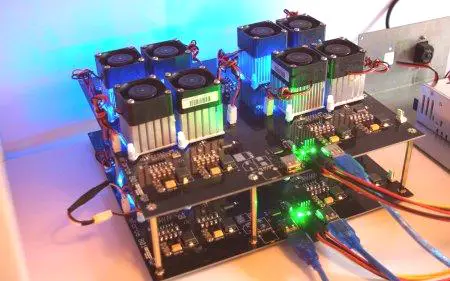

Intel Quartus Prime Software Suite Lite Edition - programska oprema za načrtovanje FPGA. Odličen je za začetnike, saj ga lahko brezplačno prenesete in ne potrebujete licence. Programsko opremo lahko prenesete na spletni strani proizvajalca. Velikost (nekaj gigabajtov)Prenos in namestitev lahko traja dlje časa. Če želite zmanjšati čas in potreben prostor na disku, priporočamo, da prenesete samo tiste elemente, ki so potrebni za opravila po meri. Na zahtevo, datoteke za prenos, odstranite kljukico "Select All" in izberite samo Quartus Prime in podporo za Cyclone V napravo. Algoritem za projekt:

Odprite novega čarovnika za projekt. Izberite Naprej & gt; Katalog & gt; & gt; Poimenujte objekt najvišje ravni.

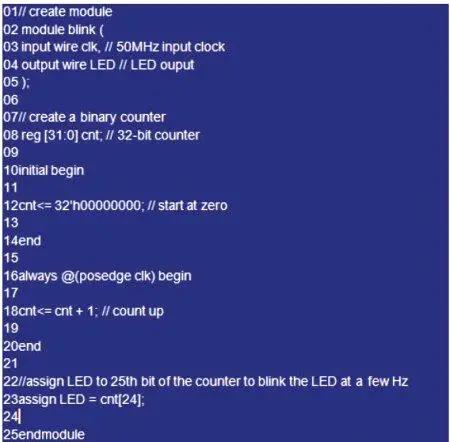

Izberite imenik za postavitev projekta, na primer "Blink" in ga postavite v mapo intelFPGA_lite, vendar ga lahko postavite kjerkoli in kliknete "Next". Ko ste pozvani, da ustvarite imenik, izberite "Da". Izberite "Empty project" in kliknite "Next". Dodajte datoteke in "Naprej". Prilagodite družino, napravo in tablo tako, da izberete naslednje: družina - Cyclone V, naprava - Cyclone V SE, osnova, ime naprave: 5CSEBA6U2317. Če želite izbrati določeno napravo, morate klikniti puščice navzgor /navzdol, da se prikaže seznam podprtih naprav, dokler se ne prikaže 5CSEBA6U2317. Uporabnik bo morda moral razširiti polje "Ime", da prikaže polno ime naprave, kliknite "Naprej". Pri nastavitvi orodja EDA se uporabljajo standardna orodja, tako da ne bo nobenih sprememb, kliknite "Naprej" in "Končano". Prikaže se zaslon s povzetkom. Ustvarite datoteko HDL z uvedbo Veriloga kot HDL. Pojdite na zavihek Datoteka (glavno okno) in izberite Novo. Izberite datoteko Verilog HDL in kliknite V redu. Izberite Datoteka & gt; »Shrani kot«.Izberite ime datoteke. To je ime datoteke najvišje ravni in mora ustrezati imenu projekta. Kliknite »Shrani«. Ustvarite modul Verilog. Kopirajte in prilepite spodnjo kodo Verilog v okno blink.v in shranite kodno datoteko. Z desno tipko miške kliknite Analiza in sinteza in nato kliknite Začni, da izvedete verifikacijo in verifikacijo sintakse Verilog.Če je postopek uspešno zaključen, se skupaj z analizo in sintezo prikaže zelena kljukica. Če je prišlo do napake, preverite skladnjo in se prepričajte, da se popolnoma ujema z zgornjim kodnim nizom. Vsi izkušeni programerji vedo, da kompleksni programi, tudi podprogrami, ne delujejo pravilno od prvega. Abstrakcijska sposobnost osebe, ki temelji na izkušnjah, mu omogoča, da najde rešitev, ne da bi skrbel za najmanjše podrobnosti. Toda stroga resnica je, da fizični sistem, v katerega je vgrajen program, zahteva, da se pred vsakim delom upošteva vsak detajl. Z razvojem programskih orodij za razvoj FPGA, predvsem od tradicionalnih dobaviteljev in neodvisnih ponudnikov orodij: Synplicity, FPGA - postaja vse bolj priljubljena iz dneva v dan. Sedaj je FPGA začela vključevati specializirano strojno opremo, s katero bi kupcu zagotovili potrebne funkcije, s čimer bi zmanjšali stroške proizvajalcev. Tako se bo v prihodnosti v prihodnosti lahko pojavila konkurenca med trdimi in poceni sistemi s prožnimi jedri. Pričakuje se, da se bodo stroški v bližnji prihodnosti zaradi priljubljenosti FPGA še bolj zmanjšalivčasih povečala. Proizvajalci so začeli eksperimentirati s konceptom vgradnje FPGA v integrirana vezja, da bi ustvarili hibridno napravo. Poudarek je še na usmerjevalnih povezavah, manjše spremembe pa so opazne v arhitekturi CLB. Ker FPGA še naprej vključujejo procesorje, nova generacija potrebuje ne le poznavanje strojne opreme digitalnega oblikovanja, ampak tudi izkušnje razvijalcev v procesu enkratnega programiranja FPGA. Na splošno se pričakuje, da bo FPGA odvzel tržni delež v napravah ASIC in postal prevladujoča tehnologija, ki zajema številne aplikacije iz različnih področij.